# **NP-SDMC Series**

# **High Current TSPD**

The NP–SDMC series of High Current Thyristor Surge Protection Devices (TSPD) protect sensitive electronic equipment from transient overvoltage conditions. The high current withstand of these devices offer protection in extreme environments and provide a solution for GR–1089 balanced "Y" configurations.

The NP-SDMC Series helps designers to comply with the various regulatory standards and recommendations including: GR-1089-CORE, IEC 61000-4-5, ITU K.20/K.21/K.45, IEC 60950, TIA-968-A, FCC Part 68, EN 60950, UL 1950.

## Features

- Low Leakage (Transparent)

- High Surge Current Capabilities

- Precise Turn on Voltages

- These are Pb-Free Devices

## **Typical Applications**

- Central Office

- Rugged Modems

- Bottom Element in "Y" Configurations

## **ELECTRICAL CHARACTERISTICS**

|               | V <sub>DRM</sub> | V <sub>(BO)</sub> | C <sub>O</sub> , 2 V,<br>1 MHz | C <sub>O</sub> , 50 V,<br>1 MHz |

|---------------|------------------|-------------------|--------------------------------|---------------------------------|

| Device        | v                | v                 | pF (Max)                       | pF (Max)                        |

| NP0720SDMCT3G | 65               | 88                | 65                             | 30                              |

| NP1300SDMCT3G | 120              | 160               | 65                             | 30                              |

| NP1500SDMCT3G | 140              | 180               | 65                             | 30                              |

| NP1800SDMCT3G | 170              | 220               | 65                             | 30                              |

| NP3100SDMCT3G | 275              | 350               | 65                             | 30                              |

G in part number indicates RoHS compliance

Other protection voltages are available upon request

Symmetrical Protection – Values the same in both negative and positive excursions (See V–I Curve on page 3)

# **ON Semiconductor®**

http://onsemi.com

# HIGH CURRENT (200A) BIDIRECTIONAL SURFACE MOUNT THYRISTOR

SMB JEDEC DO-214AA CASE 403C

## MARKING DIAGRAM

A = Assembly Location

- = Year

- WW = Work Week

- xxx = Specific Device Code

- (NPxxx0SDMC)

- = Pb-Free Package

(Note: Microdot may be in either location)

Note: Microdot may be in chiler location

## **ORDERING INFORMATION**

| Device        | Package          | Shipping <sup>†</sup> |

|---------------|------------------|-----------------------|

| NPxxxxSDMCT3G | SMB<br>(Pb-Free) | 2500 Tape &<br>Reel   |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

## **MAXIMUM RATINGS** (T<sub>A</sub> = $25^{\circ}$ C unless otherwise noted)

| Symbol           | Rating                                                                                                    | Rating Value                      |      | Unit |  |

|------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------|------|------|--|

| V <sub>DRM</sub> | Repetitive peak off-state voltage: Rated maximum                                                          | NP0720SDMCT3G                     | ±65  | V    |  |

|                  | (peak) continuous voltage that may be applied in the off-state conditions including all dc and repetitive | NP1300SDMCT3G                     | ±120 |      |  |

|                  | alternating voltage components.                                                                           | NP1500SDMCT3G                     | ±140 |      |  |

|                  |                                                                                                           | NP1800SDMCT3G                     | ±170 |      |  |

|                  |                                                                                                           | NP3100SDMCT3G                     | ±275 |      |  |

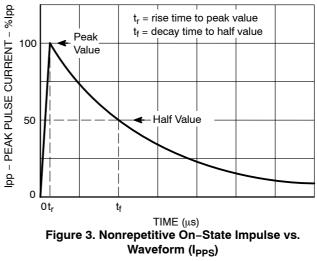

| I <sub>PPS</sub> | Nonrepetitive peak pulse current: Rated maximum value of peak impulse pulse current that may be           | 2x10 μs, GR-1089-CORE             | 1000 | А    |  |

| applied.         | 10x1000 μs, GR-1089-CORE                                                                                  | 200                               |      |      |  |

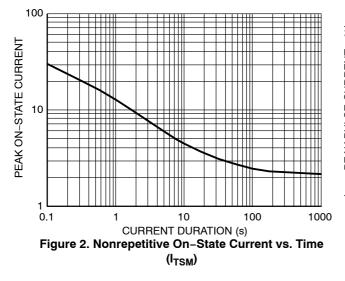

| I <sub>TSM</sub> | Non-repetitive peak on-state current: Rated                                                               | 0.0167s, 50/60 Hz, full sine wave | 60   | А    |  |

|                  | maximum (peak) value of ac power frequency<br>on-state surge current which may be applied for a           | 0.1s, 50/60 Hz, full sine wave    | 30   | A    |  |

| s                | specified time or number of ac cycles.                                                                    | 1000s, 50/60 Hz, full sine wave   | 2.2  |      |  |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## **ELECTRICAL CHARACTERISTICS TABLE** ( $T_A = 25^{\circ}C$ unless otherwise noted)

| Symbol            | Rating                                                                                                                                                                                         |                                   | Min | Тур | Max       | Unit     |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----|-----|-----------|----------|

| V <sub>(BO)</sub> | Breakover voltage: The maximum voltage across the device in or at the                                                                                                                          | NP0720SDMCT3G                     |     |     | ±88       | V        |

|                   | breakdown region.<br>V <sub>DC</sub> = 1000 V, dv/dt = 100 V/μs                                                                                                                                | NP1300SDMCT3G                     |     |     | $\pm 160$ |          |

|                   |                                                                                                                                                                                                | NP1500SDMCT3G                     |     |     | ±180      |          |

|                   |                                                                                                                                                                                                | NP1800SDMCT3G                     |     |     | $\pm 220$ |          |

|                   |                                                                                                                                                                                                | NP3100SDMCT3G                     |     |     | $\pm 350$ |          |

| I <sub>(BO)</sub> | Breakover Current: The instantaneous current flowing at the breakover v                                                                                                                        | oltage.                           |     |     | 800       | mA       |

| Ι <sub>Η</sub>    | Holding Current: The minimum current required to maintain the device in                                                                                                                        | the on-state.                     | 150 |     |           | mA       |

| I <sub>DRM</sub>  | Off-state Current: The dc value of current that results from the applica-                                                                                                                      | V <sub>D</sub> = 50 V             |     |     | 2         | mA<br>μA |

|                   | tion of the off-state voltage                                                                                                                                                                  | $V_D = V_{DRM}$                   |     |     | 5         |          |

| V <sub>T</sub>    | On–state Voltage: The voltage across the device in the on–state conditio $I_T$ = 2.2 A (pk), PW = 300 $\mu s,$ DC = 2%                                                                         | n.                                |     |     | 4         | V        |

| dv/dt             | Critical rate of rise of off-state voltage: The maximum rate of rise of volta will not cause switching from the off-state to the on-state. Linear Ramp between 0.1 $V_{DRM}$ and 0.9 $V_{DRM}$ | ge (below V <sub>DRM</sub> ) that | ±5  |     |           | kV/μs    |

| di/dt             | Critical rate of rise of on-state current: rated value of the rate of rise of cu<br>can withstand without damage.                                                                              | urrent which the device           |     |     | ±500      | A/μs     |

| CO                | Off-state Capacitance f = 1.0 MHz, $V_d$ = 1.0 V <sub>RMS</sub> , $V_D$ = -2 Vdc                                                                                                               |                                   |     |     | 65        | pF       |

## THERMAL CHARACTERISTICS

| Symbol           | Rating                                                                                                                                 | Value       | Unit |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| T <sub>STG</sub> | Storage Temperature Range                                                                                                              | –65 to +150 | °C   |

| TJ               | Operating Temperature Range                                                                                                            | -40 to +150 | °C   |

| R <sub>0JA</sub> | Thermal Resistance: Junction-to-Ambient Per EIA/JESD51-3, PCB = FR4 3"x4.5"x0.06"<br>Fan out in a 3x3 inch pattern, 2 oz copper track. | 90          | °C/W |

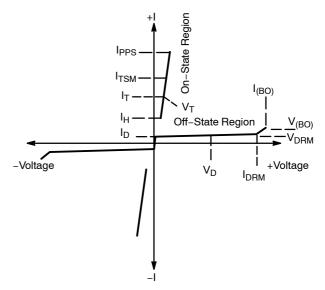

| Symbol            | Parameter                           |

|-------------------|-------------------------------------|

| V <sub>DRM</sub>  | Repetitive Peak Off-state Voltage   |

| V <sub>(BO)</sub> | Breakover Voltage                   |

| I <sub>DRM</sub>  | Off-state Current                   |

| I <sub>(BO)</sub> | Breakover Current                   |

| Ι <sub>Η</sub>    | Holding Current                     |

| V <sub>T</sub>    | On-state Voltage                    |

| Ι <sub>Τ</sub>    | On-state Current                    |

| I <sub>TSM</sub>  | Nonrepetitive Peak On-state Current |

| I <sub>PPS</sub>  | Nonrepetitive Peak Impulse Current  |

| V <sub>D</sub>    | Off-state Voltage                   |

| I <sub>D</sub>    | Off-state Current                   |

## ELECTRICAL PARAMETER/RATINGS DEFINITIONS

### **Detailed Operating Description**

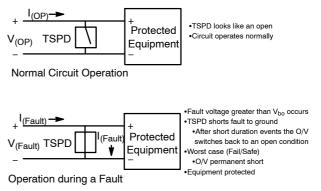

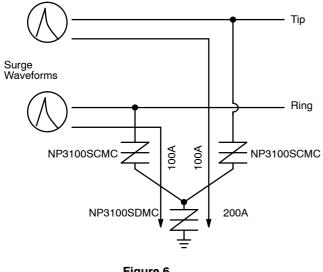

The TSPD or <u>Thyristor Surge Protection Device</u> are specialized silicon based overvoltage protectors, used to protect sensitive electronic circuits from damaging overvoltage transient surges caused by induced lightning and powercross conditions.

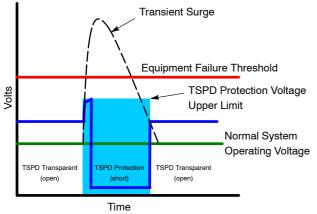

The TSPD protects by switching to a low on state voltage when the specified protection voltage is exceeded. This is known as a "crowbar" effect. When an overvoltage occurs, the crowbar device changes from a high–impedance to a low–impedance state. This low–impedance state then offers a path to ground, shunting unwanted surges away from the sensitive circuits.

This crowbar action defines the TSPD's two states of functionality: Open Circuit and Short Circuit.

<u>Open Circuit</u> – The TSPD must remain transparent during normal circuit operation. The device looks like an open across the two wire line.

Figure 1. Voltage Current Characteristics of TSPD

<u>Short Circuit</u> – When a transient surge fault exceeds the TSPD protection voltage threshold, the devices switches on, and shorts the transient to ground, safely protecting the circuit.

**Figure 4. Normal and Fault Conditions**

The electrical characteristics of the TSPD help the user to define the protection threshold for the circuit. During the open circuit condition the device must remain transparent; this is defined by the  $I_{DRM}$ . The  $I_{DRM}$  should be as low as possible. The typical value is less than 5  $\mu$ A.

The circuit operating voltage and protection voltage must be understood and considered during circuit design. The V<sub>(BO)</sub> is the guaranteed maximum voltage that the protected circuit will see, this is also known as the protection voltage. The V<sub>DRM</sub> is the guaranteed maximum voltage that will keep the TSPD in its normal open circuit state. The TSPD V<sub>(BO)</sub> is typically a 20–30% higher than the V<sub>DRM</sub>. Based on these characteristics it is critical to choose devices which have a V<sub>DRM</sub> higher than the normal circuit operating voltage, and a V<sub>(BO)</sub> which is less than the failure threshold of the protected equipment circuit. A low on–state voltage V<sub>t</sub> allows the TSPD to conduct large amounts of surge current (500 A) in a small package size.

Once a transient surge has passed and the operating voltage and currents have dropped to their normal level the TSPD changes back to its open circuit state.

TSPD's are useful in helping designers meet safety and regulatory standards in Telecom equipment including GR-1089-CORE, ITU-K.20, ITU-K.21, ITU-K.45, FCC Part 68, UL1950, and EN 60950.

ON Semiconductor offers a full range of these products in the NP series product line.

#### **DEVICE SELECTION**

When selecting a TSPD use the following key selection parameters.

#### Off-State Voltage VDRM

Choose a TSPD that has an Off–State Voltage greater than the normal system operating voltage. The protector should not operate under these conditions:

Example:

Vring = 150 Vrms = 150\*1.414 = 212 V peak

$V_{\mbox{\scriptsize DRM}}$  should be greater than the peak value of these two components:

V<sub>DRM</sub> > 212 + 48 = 260 V<sub>DRM</sub>

#### Breakover Voltage V(BO)

Verify that the TSPD Breakover Voltage is a value less than the peak voltage rating of the circuit it is protecting.

Example: Relay breakdown voltage, SLIC maximum voltage, or coupling capacitor maximum rated voltage.

#### Peak Pulse Current Ipps

Choose a Peak Pulse current value which will exceed the anticipated surge currents in testing.

#### Hold Current (I<sub>H</sub>)

The Hold Current must be greater than the maximum system generated current. If it is not then the TSPD will remain in a shorted condition, even after a transient event has passed.

# **NP-SDMC Series**

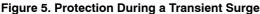

## **TYPICAL APPLICATION**

Testing: Tip – Ground . Ring – Ground Tip and Ring to Ground Simultaneously

Figure 6.

- 200 A 10 x 1000 µs Needed for GR-1089

- Bottom Element in "Y" Configuration

## NP-SDMC Series

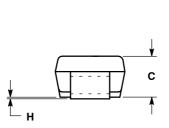

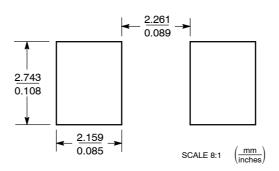

## PACKAGE DIMENSIONS

SMB

CASE 403C-01 **ISSUE A**

B

D

s

Α

NOTES:

2.

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M. 1982.

CONTROLLING DIMENSION: INCH. 3. D DIMENSION SHALL BE MEASURED WITHIN

DIMENSION P.

|     | INC       | HES    | MILLIM | ETERS |

|-----|-----------|--------|--------|-------|

| DIM | MIN MAX   |        | MIN    | MAX   |

| Α   | 0.160     | 0.180  | 4.06   | 4.57  |

| В   | 0.130     | 0.150  | 3.30   | 3.81  |

| С   | 0.075     | 0.095  | 1.90   | 2.41  |

| D   | 0.077     | 0.083  | 1.96   | 2.11  |

| Н   | 0.0020    | 0.0060 | 0.051  | 0.152 |

| J   | 0.006     | 0.012  | 0.15   | 0.30  |

| Κ   | 0.030     | 0.050  | 0.76   | 1.27  |

| Ρ   | 0.020 REF |        | 0.51   | REF   |

| S   | 0.205     | 0.220  | 5.21   | 5.59  |

#### SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILC does not convey any license under its patent rights or the rights of others. SCILC products are not designed, intended, or authorized for use a components in systems intended for surgical implant into the body, or other applications. intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative